Research

In our group - Energy-efficient Circuits and Intelligent Systems, EECIS - we focus on circuits and systems for next generation computing platforms with energy-efficient design of the key circuit blocks for a miniaturized system, optical and RF transceiver, frequency synthesizer, power management unit and data converter as well as application-specific system-level engineering for bio-medical devices and ultra-low power sensor nodes.

Research Activities and Achievements

A. Key building blocks of the miniaturized computing platform

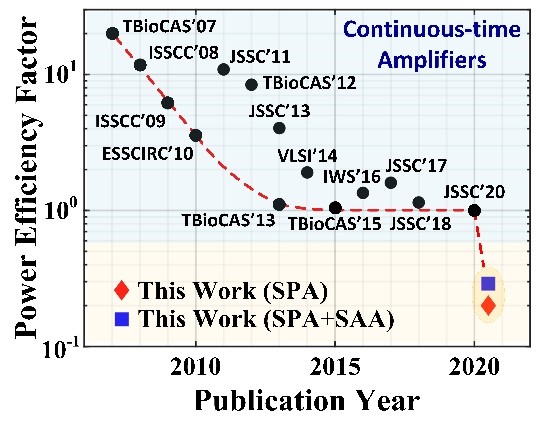

Energy-efficient analog interface: Miniaturized low-power sensor nodes for monitoring bio-signals, pressure, voice, humidity, temperature or light receive low-bandwidth μV-level signals from the sensor, demanding a power-hungry low-noise amplifier to achieve sufficiently low noise. Simultaneously, the reduced form factor of mm-sized sensor nodes places stringent limitations on their power budget, and biomedical implants must meet strict power specifications for the safety requirements on the maximum permissible heat dissipation. The EECIS group has proposed and developed discrete-time amplifiers (SPA, SAA) that achieve 5x power reduction compared to the state-of-the-art.

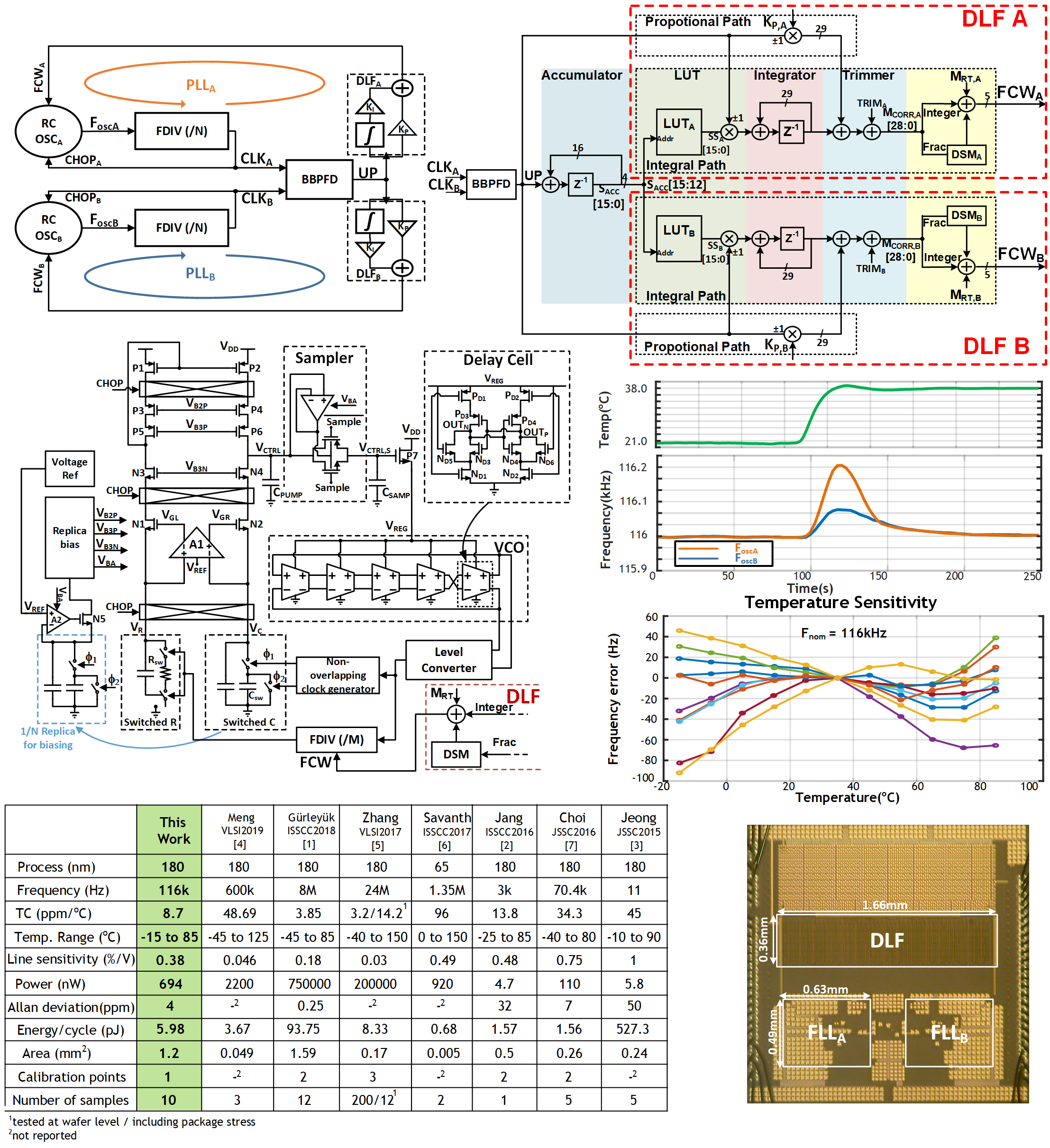

Ultra-low power timing circuits: Miniaturized computers are heavily duty-cycled to operate under the highly restricted battery capacity. Consequently, the sleep mode power dominates the total energy budget. A wake-up timer is a critical always-on component in such sleep modes and must therefore be designed with aggressive power consumption targets. At the same time, timers must also provide an accurate reference frequency in order to ensure synchronization for the communication among sensor nodes. The EECIS group has been working on developing an on-chip fully integrated clock generation circuits achieving both extremely low power consumption, and very low sensitivity to temperature variation, simultaneously. With our novel techniques such as frequency-locked loop-based clock generation, non-linearity aware temperature compensation, and delta-sigma-modulator¬-controlled oscillators, introduced in flagship conferences, the EECIS group aims at the development of nano-watt on-chip timer achieving the accuracy of crystal oscillators.

Area-efficient power converter: Over the past years, the constant reduction in the size of consumer electronics has strengthened the demand for fully integrated high-density power management circuits for IoT and mobile applications. The EECIS group has proposed and developed a new, fully integrated DC-DC converter topology based on electromagnetically coupled class-D oscillators. By operating at a high switching frequency (> GHz), the design can aggressively scale down the on-chip passives so to achieve high power density (> 1W/mm2).

Wireless communication: Modern communication systems rely on ultra-low jitter performance (<100fs) of the frequency synthesizers while maintaining a low power consumption. The EECIS group has introduced a new frequency synthesizer architecture that achieves phase feedback at the output frequency, much faster than the conventional PLLs operating at a reference frequency. This significantly reduces the output jitter, the reference spurs, and the power consumption.

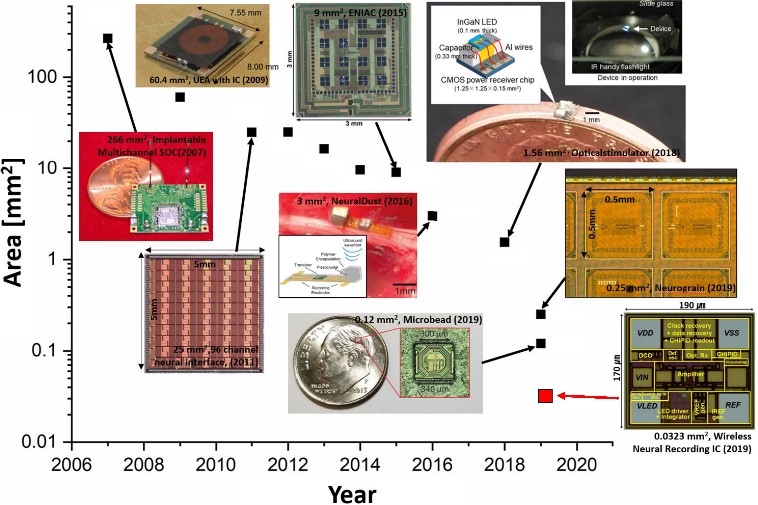

B. Neural recording system

The EECIS presented a wireless neural recording platform using the smallest stand-alone wireless neural recording unit. In this design, we developed a 0.19×0.17 mm2 semiconductor integrated circuit that is able to collect extracellular action potential signals from an 8 µm-thick carbon fiber electrode inserted in the motor cortex of a non-human primate and a Long Evans rat. In vivo evaluation of the miniaturized system showed that it consumed the lowest power reported, 740 nano-watts while retaining accurate neural signal collection. Furthermore, this platform included novel symbol interval modulation and analog data compression circuits that successfully reduced the data rate down to 800 bps (40x smaller than the raw data), saving significant data communication power. This compression exploited a new decoding algorithm, spiking band power, and achieved accurate figure position and velocity decoding with 920× power reduction compared with the state-of-the-art systems.

Ultra-low-power Timer

A precise timing reference is one of the key elements for digital systems, analog front-ends, communication systems and wireless sensor nodes. A monolithic on-chip oscillator is an attractive choice for the reduction of system volume, power consumption and cost.

Read more.

Energy-efficient Parametric Low-noise Amplifier

Miniaturized low-power wireless systems equipped with sensing, computing and communication capabilities enable a wide variety of applications in the IoT era, ranging from environmental monitoring to healthcare. In this context, maximizing the energy efficiency while preserving the desired performance is a critical design issue, as the available energy is strictly limited by the requirements on the form factor.