Ultra-low-power Timer

A precise timing reference is one of the key elements for digital systems, analog front-ends, communication systems and wireless sensor nodes. A monolithic on-chip oscillator is an attractive choice for the reduction of system volume, power consumption and cost.

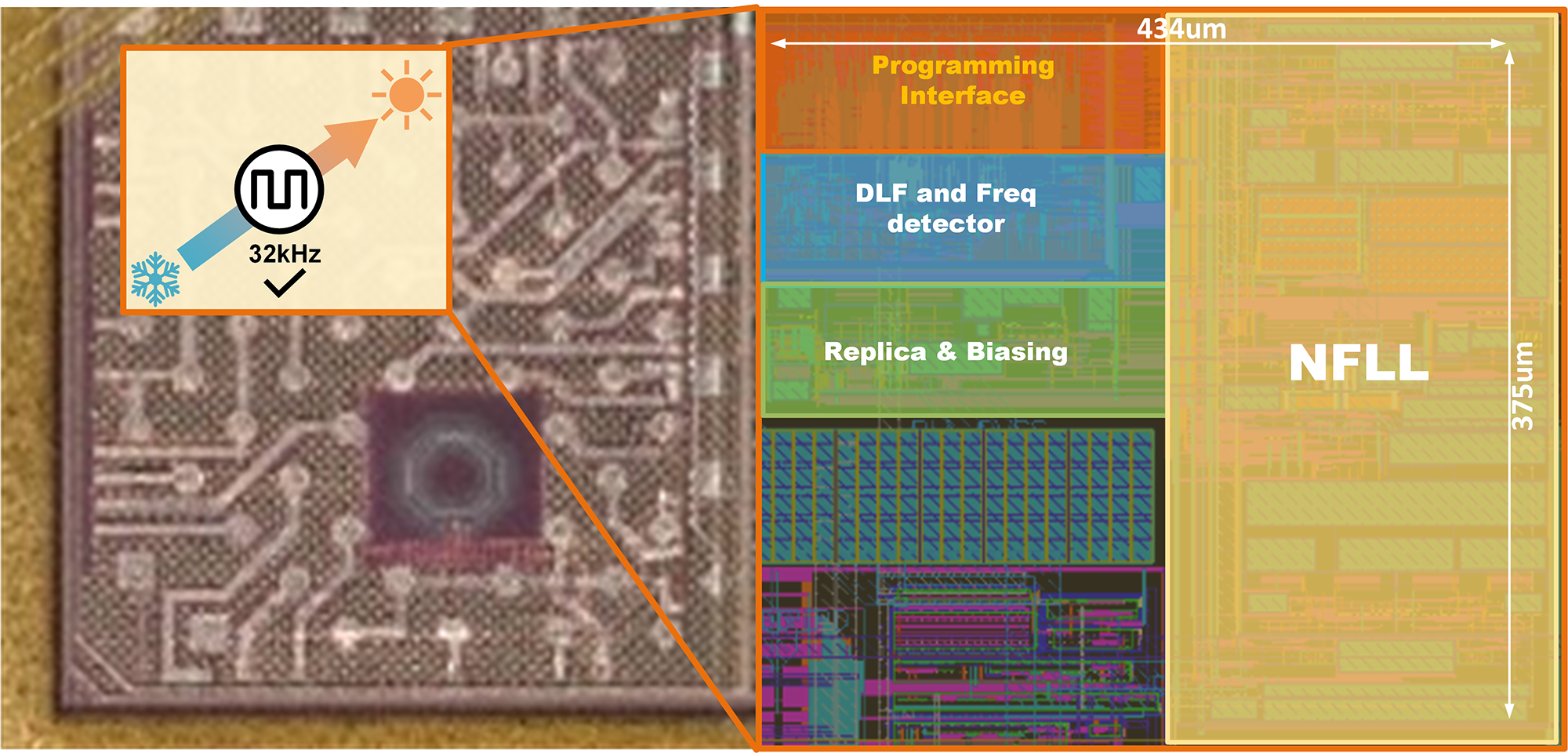

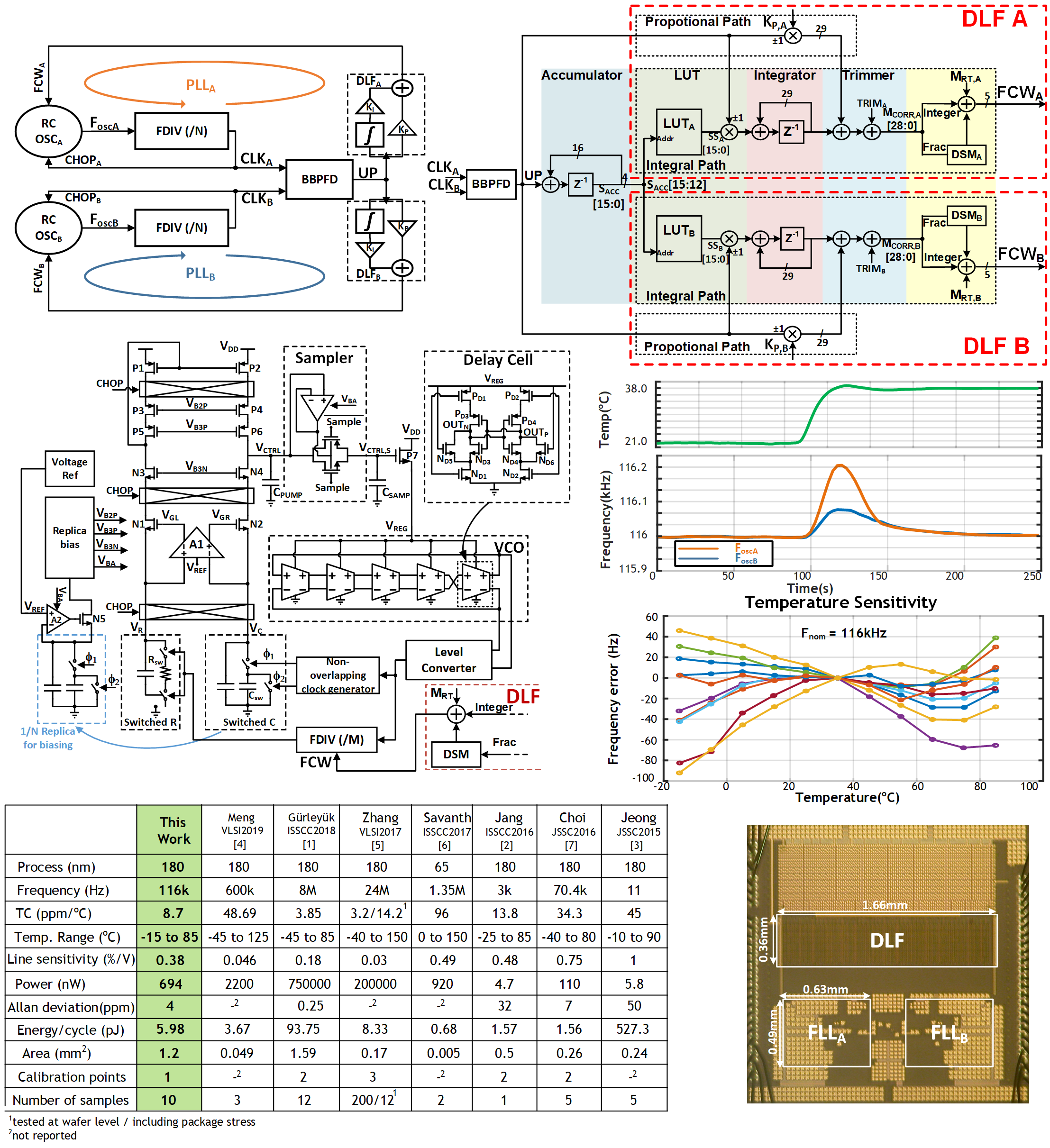

The proposed design is an ultra-low-power on-chip timer which is resilient to temperature variation across a wide temperature range. The timer employs DSM-controlled RC oscillators and a non-linearity-aware digital dual phase-locked loop. The two oscillators equipped with different types of resistors generate different temperature-dependent periods. The dual PLL equalizes the frequencies of the two FLLs by adopting an integral path gain proportional to the oscillators’ temperature coefficients, so to achieve insensitivity to temperature. The proposed design can achieve 5.86ppm/°C while consuming 0.49μW.